PCB 设计

直接参考余博士视频即可。

关于 Cadence 的教程网上已经多如牛毛,多数都大同小异,相信大部分人都是从于博士的教程中学习,于博士的教程非常的规矩完善。我写这个系列的目的是为了记录在使用 Cadence 软件中收集到的一些便捷操作,在一定程度上减少人的工作。

- Allegro快捷键修改

- PCB设计Checklists(投板前确认)

- [Allegro推荐颜色]

- Allegro 制作LOGO方法

- Allegro中的复制粘贴(模块化复用)

- Capture 中正则表达式替换

- Allegro Skill介绍及用法

- Allegro 光绘设置)

下面放上一些之前写过的教程:

Allegro快捷键修改

快捷键文件位置

在安装Cadence的时候,会选择两个目录,一个是软件安装目录,另外一个是用户环境目录,存储快捷键的的文件就在用户环境目录下,具体查找的方法如下:

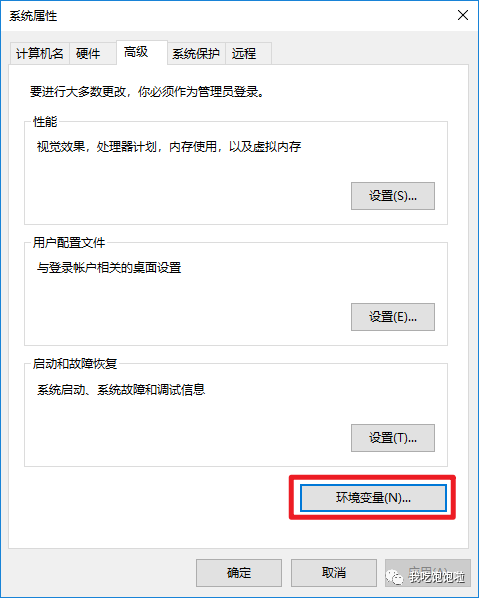

- 打开计算机属性(桌面上对着我的电脑右键->属性)

- 然后点击高级系统设置

- 在弹出来的对话框里点击环境变量,会弹出一个选项卡

- 在选项卡的用户变量里面找到Home,这就是用户变量所在的位置。

打开HOME所在的路径,如上图所示,如果安装的时候没有修改环境变量的路径,那么路径应该和上面的一样,只是用户名不一样。

打开HOME所在的路径,如上图所示,如果安装的时候没有修改环境变量的路径,那么路径应该和上面的一样,只是用户名不一样。

然后打开路径中的pcbenv文件件,里面会有一个env文件(这个文件没有扩展名),如果没有这个文件说明是第一次安装Cadence,还没有在Allegro中设置过器件的路径。可以手动创建一个env文件或者在Allegro中设置一下器件路径。

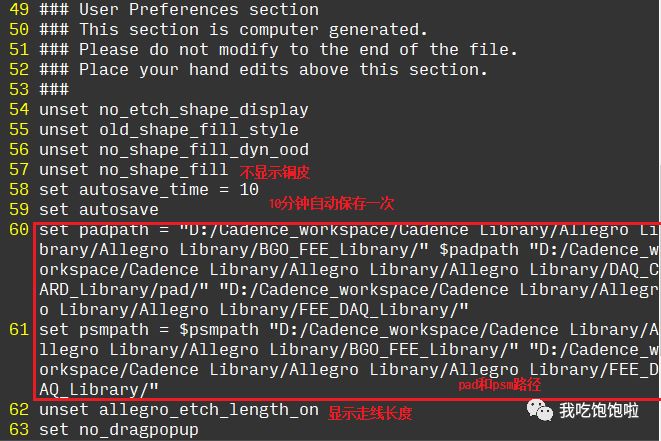

用vim、NotePad++之类的文本编辑器打开这个文件(txt编辑器也行),如果是Allegro创建的env文件,那么会有如下类似的内容,在Allegro-> Setup-> User Preference中设置的内容都会被存在这个位置,所以如果重装了Cadence,把这个文件备份到新的安装环境中,之前的用户偏好还会被记录下来。

下面是我的env中用户偏好的说明

快设置快捷键

在文件中source $TELENV后面插入需要的快捷键,快捷键可以用两个命令指定:

funckey key function:key就是按下的快捷键,function就是功能,比如funckey q add connect,按下q键之后就会进入连线命令,类似的funckeyv delete,funckey Esc oops,funckey g move都是一些常见的快捷键。注意不要用x作为快捷键,因为x要用来指定坐标。

alias key function:主要是用来指定Ctrl键+字母的快捷键,如alias ~Q add line是Ctrl+Q执行add line

常用快捷键

基本功能:包括连线、删除、撤销…

- funckey d done

- funckey v delete

- funckey n next

- funckey g move

- funckey q add connect

- funckey w slide

- funckey c cancel

- funckey r rotate

- funckey m mirror

- funckey Esc oops

- funckey l Add Line

- funckey e copy

- funckey t Text Edit

- funckey y Add Text

- funckey f Create Fanout

更换走线层:下面是一个最多支持12层板的快捷键,更多层板接着添加就好了

- funckey 11 'pop swap;subclass top'

- funckey 22 'pop swap;subclass top;+'

- funckey 33 'pop swap;subclass top;+;+'

- funckey 44 'pop swap;subclass top;+;+;+'

- funckey 55 'pop swap;subclass top;+;+;+;+'

- funckey 66 'pop swap;subclass top;+;+;+;+;+'

- funckey 77 'pop swap;subclasstop;+;+;+;+;+;+'

- funckey 88 'pop swap;subclasstop;+;+;+;+;+;+;+'

- funckey 99 'pop swap;subclasstop;+;+;+;+;+;+;+;+'

- funckey aa 'pop swap;subclasstop;+;+;+;+;+;+;+;+;+'

- funckey bb 'pop swap;subclasstop;+;+;+;+;+;+;+;+;+;+'

- funckey 00 'pop swap;subclass bottom'

选择过孔:注意过孔名字要一一对应

- funckey z0 FORM mini padstack_list VIA8_BGA

- funckey z1 FORM mini padstack_list VIA_8

- funckey z2 FORM mini padstack_list VIA10-N

- funckey z3 FORM mini padstack_list VIA12-N

- funckey z4 FORM mini padstack_list VIA16D28

- funckey z5 FORM mini padstack_list VIA24

- funckey z6 FORM mini padstack_list VIA40

改变线宽

- funckey b4 Options acon_line_width 4

- funckey b6 Options acon_line_width 6

- funckey b8 Options acon_line_width 8

- funckey b10 Options acon_line_width 10

- funckey b16 Options acon_line_width 16

- funckey b24 Options acon_line_width 24

- funckey b040 Options acon_line_width 40

注意最后一个用的是b040,因为如果用b40的话,在按下b4之后就会执行线宽为4mil的操作。

设置完快捷键之后保存重启Allegro就可以生效了。

最重要的快捷键Ctrl + S!!!

PCB设计Checklists(投板前确认)

做了一个简单的Checklists,不断完善中

| No | Item | Answer (Y/N/NA) | Notes |

|---|---|---|---|

| 原理图 | |||

| 1 | 电源分配是否正确? | ||

| 2 | 电源电压是否正确? | ||

| 3 | FPGA电源滤波是否按照要求设置? | ||

| 4 | 电源芯片输出和电源平面是否通过Pi型滤波隔离? | ||

| 5 | 每个器件管脚编号和用途是否正确? | ||

| 6 | 每个器件的管脚是否按照要求滤波? | ||

| 7 | 每个器件电源电压是否正确? | ||

| 8 | 连接器的外壳是否通过磁珠接地? | ||

| 9 | 各个芯片 Checklists 是否通过? | ||

| 10 | FPGA的 M[2:0] 是否通过电阻连接并正确设置? | ||

| 11 | FPGA的 PROGRAM_B 是否 4.7k Ohm 上拉 | ||

| 12 | FPGA DONE 是否上拉? | ||

| 13 | PUDC_B是否上拉或下拉? | ||

| 14 | INIT_B是否 4.7k Ohm 上拉 | ||

| 15 | Flash的 D[3:0] 和 CS 是否上拉 | ||

| 16 | FPGA 上电顺序是否正确? VCCINT -> VCCBRAM -> VCCAUX -> VCCO | ||

| 17 | 高速部分上电顺序是否正确?VCCINT -> VMGTAVCC-> VMGTAVTT 或者VMGTAVCC -> VCCINT -> VMGTAVTT | ||

| 18 | Flash大小是否合适 | ||

| 19 | 差分信号 bank电压是否正确? HP bank 1.8V / HR bank 2.5V | ||

| 20 | 如果不用上门的电压,是否只用作接收,并且100 Ohm匹配 | ||

| 21 | DRC检查是否通过? | ||

| 22 | 是否没有 Warnning? | ||

| 23 | 器件是否购买? | 原理图接近尾声的时候买器件 | |

| PCB | |||

| 1 | 坐标原点是否是左边的边和下边的边的交点? | 强制 | |

| 2 | 是否倒角? | 建议 | |

| 3 | 地平面是否比版边缘缩进 20mil? | 存疑 | |

| 4 | 电源平面是否比地平面缩进 40mil? | 存疑 | |

| 5 | 机械孔接地还是不接地,是否正确使用机械孔? | ||

| 6 | 层叠结构是否对称? | 如不对称,和制版商确认残铜率 | |

| 7 | 每个信号层是否都有参考平面? | 低速信号可无参考 | |

| 8 | 信号线宽是否一致? | ||

| 9 | 差分对是否正确设置? | ||

| 10 | 差分对是否等长? | ||

| 11 | 芯片的滤波电容是否靠近芯片? | ||

| 12 | FPGA 的 VCC_INT 的滤波电容是否放在芯片下面? | ||

| 13 | CCLK 信号完整性是否保证? | ||

| 14 | 顶层和底层走线没有穿过电容电阻焊盘? | ||

| 15 | 芯片 TAB 是否打孔到相应电源层? | ||

| 16 | 芯片电源管脚是否是否用宽走线连出? | ||

| 17 | 电源过孔电流是否满足要求? | ||

| 18 | 地平面没有被割出狭缝? | ||

| 19 | 走线线宽是否满足 3W? | ||

| 20 | 是否在板空余位置打上 GND 孔? | ||

| 21 | FPGA 高速信号是否隔离? | ||

| 22 | FPGA 时钟输入是否接到专用时钟管脚? | ||

| 23 | 所有电源焊盘和铜平面都有良好接触? | ||

| 24 | 连接器座子方向是否确认?HDMI, USB | ||

| 25 | 所有焊盘都有 Flash? | ||

| 26 | 每个检查是否通过? | ||

| 27 | Database Check 是否通过? | ||

| 28 | 是否加上板名、日期和设计者? | ||

| 29 | 出光绘前是否钻孔? | ||

| 30 | 出光绘后是否用 CAM 350 查看? | ||

| 31 | 出光绘后是否查看 Warnning? | ||

| 32 | 自己画的封装是否1:1打印和器件进行对比? | ||

| 33 | 最后一次出光绘前是否删除文件夹下除 brd 外其他文件? | ||

| 34 | 最后一次出光绘前是否做各种 Report? | ||

| 35 | 最后一次出光绘前是否重新生成钻孔? | ||

| 36 | 光绘 Warning 是否只有边框线宽的 Warning? |

[Allegro推荐颜色]

Allegro 提供不同的颜色将不同的 subclass 的颜色区分开有助于 PCB 设计,不同人有不同的配色标准,本无不可,但是相互之间查看电路板还是会带来障碍,因此在这里提供一种配色方案,希望大家都采用。

ETCH

Top 红色

Signal1 天蓝色

Signal2 橘黄色

Signal3 粉红色

多的内电层颜色请自定义鲜艳的颜色

Bottom 层深蓝色

Net

- 目前只规定GND的颜色为青青草原色

- 电源请自行选择鲜艳颜色,可以和 ETCH 的颜色重复

其他辅助层

Top 层丝印白色 , Bottom 层丝印黄色

Allegro 制作LOGO方法

Allegro中的复制粘贴(模块化复用)

模块化设计时Allegro中的一个重要的思想,在大量重复电路的设计中可以减少很多的工作量。 用Google直接搜索Allegro模块化设计就可以出来很多的关于模块化设计的教程,能找到的教程是从Capture开始做模块化设计的,也就是先在Capture中设计好模块的原理图,做好DRC检查,然后在Allegro中设计好该模块的布局布线,接下来就可以在Capture中反复调用这个模块,然后Allegro中也可以像摆放元器件那样摆放该模块。 这样的方法适用于模块高度一致的情况,可以很方便的设计原理图和PCB,网上的教程也非常多;这种方法的缺点是如果要修改其中的一个模块,那么所有的模块都会相应的被修改。 接下来我要介绍一种在Allegro中进行模块化设计的方法,这个方法就相当于复制粘贴一样,粘贴后的模块可以独立修改,当然这个方法的缺点是有多少个模块就要在原理图中画多少个。

原理图绘制

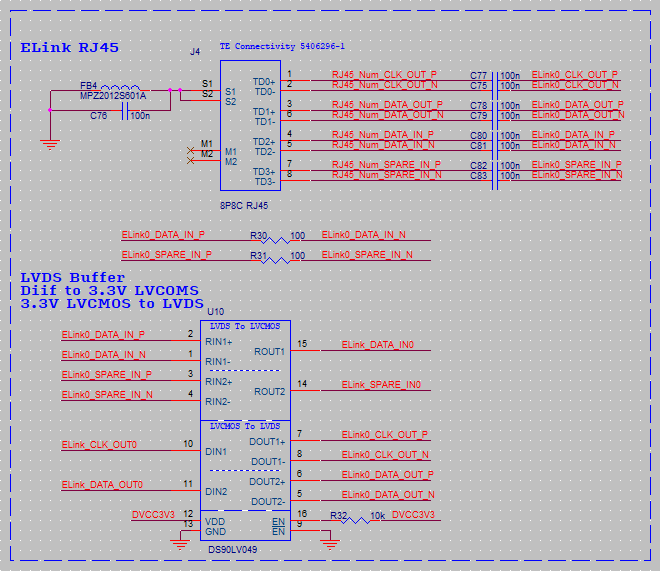

在Capture中首先要保证需要模块化的原理图是一致的,包括元器件、封装、值(特别是电容电阻的值,如果不一致的话会稍微麻烦一点)。下面以这样一个模块为例,先设计好一个模块,然后复制很多遍(复制很多遍是一个不好的做法,更好的方法以后介绍)

Allegro设计

在Allegro中对要复制的部分进行设计,将布局布线做好,包括丝印也一起调整好,模块化的时候丝印的大小和位置也会一起做到模块中,一个布局布线好的模块如下图所示

然后在Allegro的右下角位置处找到 General edit,点击这个位置,在浮出的选框中选择Placement edit,如下图所示

在Find中点击All on,选中所有要模块化的部分,右键单击,点击Place replicate create,然后右键Done,左键单击一次,之后会弹出一个框,保存文件成需要的名字,这里保存的就是模块化需要的信息,操作见下面的动图

做好模块之后,下面就是应用模块。首先是将需要摆放的元件放在一堆,随意摆放即可,然后选中所有的元件,右键单击,在Place replicate apply的次级选项中选择刚刚保存好的模块名,所有的元件都会被摆好,包括连线、打孔和丝印,这些部分会成为一个模块,摆放到合适的位置即可,如果要整个模块一起移动,在Find里选择Group即可。操作见下面的动图

如果有些元件的Value和做好的模块不一致,Allegro不能够自动识别,会弹出一个框,手动选择元器件之间的对应关系即可。

Capture 中正则表达式替换

替换 TCL 介绍

capture 提供了一系列的脚本可供操作,下面介绍一种会经常用到的功能——替换。

这个替换脚本的功能是让设计者可以很方便的替换页面上的文本、alias、off-page connector 和 ports。

添加 TCL 路径

首先是在 Capture 的命令窗口中添加 TCL 的路径,输入source D:/Cadence/SPB_16.6/tools/capture/tclscripts/capDB/capDesignUtil.tcl 即可。

如果没有命令窗口的话,在 View -> Command Window 打开

然后在文件管理器里面的地址栏输入 D:/Cadence/SPB_16.6/tools/capture/tclscripts/capDB/capDesignUtil.tcl

然后在文件管理器里面的地址栏输入 D:/Cadence/SPB_16.6/tools/capture/tclscripts/capDB/capDesignUtil.tcl

用一个文本编辑器打开这个文件,哪怕是 TXT 也行。这一步主要目的是为了方便查看具体的命令。

替换命令

从手册中查两个命令

- 在当前页面替换 Alias

**::capDesignUtil::capVisitPageAliases [GetActivePage] Replace** <待替换的 Alias 名> <替换成的 Alias 名>

- 在当前页面替换 Ports

**::capDesignUtil::capVisitPagePorts [GetActivePage] Replace** <待替换的 Ports 名> <替换成的 Ports 名>

连同 :: 在内的语句就是替换的语法,手册中还有其他语法的用法,类比即可。 这个语法的最大的好处是支持正则表达式,可以比更灵活的应用于更多模块的开发,比如说下面的这个例子:

有一片差分时钟芯片,10个输出,按照命名的设想,每个输出应当设置为CLK_OUTNum_P和CLK_OUTNum_N,这样在以后设置差分对的时候能够方便的识别差分对的名字。

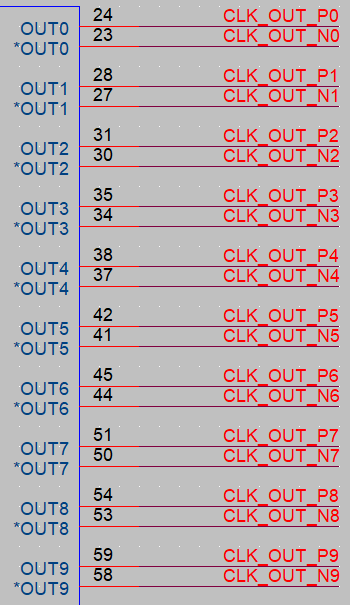

但是这样子设置名字的话,10对差分对就要手动输入20次,极大的增加了工作量,一个好的做法是,先将名字设置为 CLK_OUT_P0~9,CLK_OUT_N0~9,如下图所示,这样起名字的好处是可以利用Net Alias的自增功能,然后再调用替换脚本。

在命令窗口输入如下命令

::capDesignUtil::capVisitPageAliases [GetActivePage] Replace {(CLK_OUT)_(P|N)(\d)} {\1\3_\2}

命令的替换和被替换的内容是使用正则表达式来匹配的,第一个大括号内的内容就是待匹配的内容,表示匹配上CLK_OUT_P+数字或者CLK_OUT_N+数字,然后第二个大括号调整他们的顺序,\1\2\3表示第一个大括号里面的三个小括号对应的内容。效果如下

同理Ports也可以替换,下面这个例子是替换一个SFP座子的Ports,设计中先设计好一个模板,然后可以批量复制,然后把Ports和NetAlias替换成对应的名称即可

懒惰即是第一生产力。

Allegro Skill介绍及用法

Allegro skill介绍

Skill 是Cadence 提供的可第二次开发的语言。语法同C语言类似。在设计中使用skill可以大大简化PCB绘制流程,还可以定制各种各样的功能。

本文只对skill使用做一个简单的介绍,进阶的方面以后学会再做笔记。

推荐一个网站:Allegro Skill,使用的skill和介绍均来自此网站

Allegro skill设置方法

以一个skill为例(ch_via_net),这个skill的功能是将电路板中的过孔的网络修改为任意一个网络。

先从任何一个地方获取到这个skill文件ch_via_net.il。

将文件放置在一个文件夹中,不含中文和空格。如我放置在D:\Cadence\skill中,方便日后管理

在环境变量文件夹中找到allegro.ilinit文件,这个文件一般在C:\Users\AppData\Roaming\SPB_Data\pcbenv中,表示计算机用户名。

- 如果在上一步找不到这个文件的话说明从来都没有程序创建过这样一个文件,自己创建一个文件名为 allegro.ilinit 的文件;如果在安装的时候修改了用户变量的位置,就直接搜索 SPB_DATA 所在的文件夹

编辑这个文件,在文件中加入如下的代码 setSkillPath(buildString(append1(getSkillPath() "D:/Cadence/skill"))) ;设置skill所在路径 load("ch_via_net.il" "www.allegro-skill.com") ;载入skill 前一个参数是skill文件,后一个是密码。

Skill设计结束,可以在工程中使用了。

最好为skill的操作设置一个快捷键,不然使用中不会很方便。

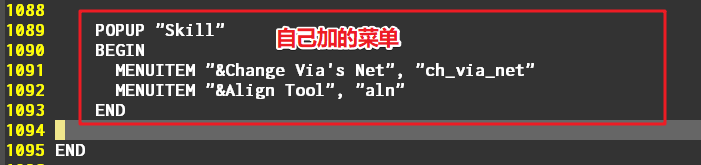

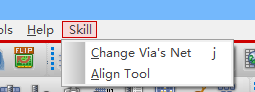

可以自定义allegro菜单,将自己添加的skill加入菜单中方便使用 在安装路径D:\Cadence\SPB_16.6\share\pcb\text\cuimenus中找到allegro.men文件,该文件为加载目录文件。在目录的最后一个end前加入如下代码:

POPUP "My_Skill"

BEGIN

MENUITEM "&Chang Via's Net", "ch_via_net"

END

其他 skill 请前往 Allegro Skill 网站下载